Ich habe mir gebrauchte Hardware neu zugelegt, ein MSI B450-A PRO MAX Motherboard mit Ryzen 5 3600 und 32GB RAM ..von Kleinanzeigen.

Um zu testen was ich da bekommen habe, liegt der Kram hier auf dem Tisch, mit einer 1TB Barracuda, vom Stick 12.2-stable installiert mit git ports und src gezogen und das Ding compiliert mit erstaunlicher Lebendigkeit gleichzeitig 2x den llvm, einmal für die world und einmal X11 aus den Ports..

So weit so hübsch.

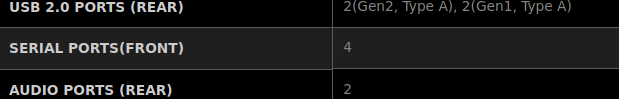

Ich habe schon beim Überfliegen des Handbuchs festgestellt das das Mainboard über eine Parallelschnittstelle und eine UART verfügt. Sehr gut, aber was zur Hölle ist denn das hier:

(dmesg|less)

--schnipp--

isab0: <PCI-ISA bridge> at device 20.3 on pci0

isa0: <ISA bus> on isab0

acpi_button0: <Power Button> on acpi0

uart2: <16x50 with 256 byte FIFO> iomem 0xfedc9000-0xfedc9fff,0xfedc7000-0xfedc7fff irq 3 on acpi0

uart3: <16x50 with 256 byte FIFO> iomem 0xfedca000-0xfedcafff,0xfedc8000-0xfedc8fff irq 4 on acpi0

uart4: <16x50 with 256 byte FIFO> iomem 0xfedce000-0xfedcefff,0xfedcc000-0xfedccfff irq 3 on acpi0

uart5: <16x50 with 256 byte FIFO> iomem 0xfedcf000-0xfedcffff,0xfedcd000-0xfedcdfff irq 4 on acpi0

ppc1: <Parallel port> port 0x378-0x37f irq 5 on acpi0

ppc1: Generic chipset (NIBBLE-only) in COMPATIBLE mode

ppbus0: <Parallel port bus> on ppc1

lpt0: <Printer> on ppbus0

lpt0: Interrupt-driven port

ppi0: <Parallel I/O> on ppbus0

atkbdc0: <Keyboard controller (i8042)> port 0x60,0x64 irq 1 on acpi0

atkbd0: <AT Keyboard> irq 1 on atkbdc0

kbd0 at atkbd0

atkbd0: [GIANT-LOCKED]

uart0: <16550 or compatible> port 0x3f8-0x3ff irq 4 flags 0x10 on acpi0

hwpstate0: <Cool`n'Quiet 2.0> on cpu0

ZFS filesystem version: 5

ZFS storage pool version: features support (5000)

---schnapp---

Ich sehe da 5 uarts, wo kommen die denn her? Prompt gibts auch die entsprechenden Einträge in /dev

# ls -l /dev/cu*

crw-rw---- 1 uucp dialer 0x58 Nov 16 19:47 /dev/cuau0

crw-rw---- 1 uucp dialer 0x59 Nov 16 19:47 /dev/cuau0.init

crw-rw---- 1 uucp dialer 0x5a Nov 16 19:47 /dev/cuau0.lock

crw-rw---- 1 uucp dialer 0x3a Nov 16 19:47 /dev/cuau2

crw-rw---- 1 uucp dialer 0x3b Nov 16 19:47 /dev/cuau2.init

crw-rw---- 1 uucp dialer 0x3c Nov 16 19:47 /dev/cuau2.lock

crw-rw---- 1 uucp dialer 0x40 Nov 16 19:47 /dev/cuau3

crw-rw---- 1 uucp dialer 0x41 Nov 16 19:47 /dev/cuau3.init

crw-rw---- 1 uucp dialer 0x42 Nov 16 19:47 /dev/cuau3.lock

crw-rw---- 1 uucp dialer 0x46 Nov 16 19:47 /dev/cuau4

crw-rw---- 1 uucp dialer 0x47 Nov 16 19:47 /dev/cuau4.init

crw-rw---- 1 uucp dialer 0x48 Nov 16 19:47 /dev/cuau4.lock

crw-rw---- 1 uucp dialer 0x4c Nov 16 19:47 /dev/cuau5

crw-rw---- 1 uucp dialer 0x4d Nov 16 19:47 /dev/cuau5.init

crw-rw---- 1 uucp dialer 0x4e Nov 16 19:47 /dev/cuau5.lock

Soweit ich das beim quer lesen mitbekommen habe weiß das Manual des Boards von einer Uart und dafür

gibts auch einen 10poligen Header auf der Platine, was ist denn der Rest?

Gruß,

Holm

Um zu testen was ich da bekommen habe, liegt der Kram hier auf dem Tisch, mit einer 1TB Barracuda, vom Stick 12.2-stable installiert mit git ports und src gezogen und das Ding compiliert mit erstaunlicher Lebendigkeit gleichzeitig 2x den llvm, einmal für die world und einmal X11 aus den Ports..

So weit so hübsch.

Ich habe schon beim Überfliegen des Handbuchs festgestellt das das Mainboard über eine Parallelschnittstelle und eine UART verfügt. Sehr gut, aber was zur Hölle ist denn das hier:

(dmesg|less)

--schnipp--

isab0: <PCI-ISA bridge> at device 20.3 on pci0

isa0: <ISA bus> on isab0

acpi_button0: <Power Button> on acpi0

uart2: <16x50 with 256 byte FIFO> iomem 0xfedc9000-0xfedc9fff,0xfedc7000-0xfedc7fff irq 3 on acpi0

uart3: <16x50 with 256 byte FIFO> iomem 0xfedca000-0xfedcafff,0xfedc8000-0xfedc8fff irq 4 on acpi0

uart4: <16x50 with 256 byte FIFO> iomem 0xfedce000-0xfedcefff,0xfedcc000-0xfedccfff irq 3 on acpi0

uart5: <16x50 with 256 byte FIFO> iomem 0xfedcf000-0xfedcffff,0xfedcd000-0xfedcdfff irq 4 on acpi0

ppc1: <Parallel port> port 0x378-0x37f irq 5 on acpi0

ppc1: Generic chipset (NIBBLE-only) in COMPATIBLE mode

ppbus0: <Parallel port bus> on ppc1

lpt0: <Printer> on ppbus0

lpt0: Interrupt-driven port

ppi0: <Parallel I/O> on ppbus0

atkbdc0: <Keyboard controller (i8042)> port 0x60,0x64 irq 1 on acpi0

atkbd0: <AT Keyboard> irq 1 on atkbdc0

kbd0 at atkbd0

atkbd0: [GIANT-LOCKED]

uart0: <16550 or compatible> port 0x3f8-0x3ff irq 4 flags 0x10 on acpi0

hwpstate0: <Cool`n'Quiet 2.0> on cpu0

ZFS filesystem version: 5

ZFS storage pool version: features support (5000)

---schnapp---

Ich sehe da 5 uarts, wo kommen die denn her? Prompt gibts auch die entsprechenden Einträge in /dev

# ls -l /dev/cu*

crw-rw---- 1 uucp dialer 0x58 Nov 16 19:47 /dev/cuau0

crw-rw---- 1 uucp dialer 0x59 Nov 16 19:47 /dev/cuau0.init

crw-rw---- 1 uucp dialer 0x5a Nov 16 19:47 /dev/cuau0.lock

crw-rw---- 1 uucp dialer 0x3a Nov 16 19:47 /dev/cuau2

crw-rw---- 1 uucp dialer 0x3b Nov 16 19:47 /dev/cuau2.init

crw-rw---- 1 uucp dialer 0x3c Nov 16 19:47 /dev/cuau2.lock

crw-rw---- 1 uucp dialer 0x40 Nov 16 19:47 /dev/cuau3

crw-rw---- 1 uucp dialer 0x41 Nov 16 19:47 /dev/cuau3.init

crw-rw---- 1 uucp dialer 0x42 Nov 16 19:47 /dev/cuau3.lock

crw-rw---- 1 uucp dialer 0x46 Nov 16 19:47 /dev/cuau4

crw-rw---- 1 uucp dialer 0x47 Nov 16 19:47 /dev/cuau4.init

crw-rw---- 1 uucp dialer 0x48 Nov 16 19:47 /dev/cuau4.lock

crw-rw---- 1 uucp dialer 0x4c Nov 16 19:47 /dev/cuau5

crw-rw---- 1 uucp dialer 0x4d Nov 16 19:47 /dev/cuau5.init

crw-rw---- 1 uucp dialer 0x4e Nov 16 19:47 /dev/cuau5.lock

Soweit ich das beim quer lesen mitbekommen habe weiß das Manual des Boards von einer Uart und dafür

gibts auch einen 10poligen Header auf der Platine, was ist denn der Rest?

Gruß,

Holm